Modeling and Verification of Asynchronous Systems Using Timed Integrated Model of Distributed Systems

Sensors | Free Full-Text | Modeling and Verification of Asynchronous Systems Using Timed Integrated Model of Distributed Systems

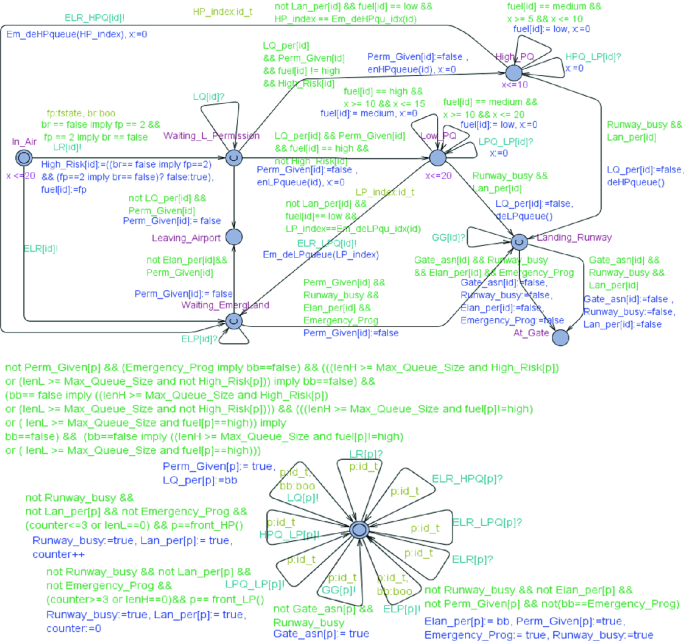

Integration of iUML-B and UPPAAL Timed Automata for Development of Real-Time Systems with Concurrent Processes | SpringerLink

Sensors | Free Full-Text | Bounded Model Checking for Metric Temporal Logic Properties of Timed Automata with Digital Clocks

modeling - UPPAAL: Invariants violated but none have been explicitly set - how to resolve deadlock? - Stack Overflow

Integration of iUML-B and UPPAAL Timed Automata for Development of Real-Time Systems with Concurrent Processes | SpringerLink